Verilog Simulation Example act as a vibrant component of the video gaming experience, supplying players an opportunity to improve their in-game adventures. These alphanumeric combinations serve as digital secrets, unlocking a treasure of exclusive products, money, or other interesting attributes. Game developers utilize codes as a means to promote community involvement, celebrate landmarks, or promote special occasions, developing a special and interactive link between developers and gamers.

How to Retrieve Codes

Verilog Simulation Example

Verilog Simulation Example -

Retrieving Verilog Simulation Example is a simple procedure that adds an additional layer of contentment to the gaming experience. As you embark on your virtual trip, comply with these basic steps to assert your incentives:

- Introduce the Game: Start your pc gaming session by firing up the Roblox game where you desire to retrieve the code.

- Situate the Code Redemption Area: Navigate through the game's user interface to find the dedicated code redemption area. This may be within the game's settings, a details menu, or an assigned website.

- Enter the Code: Carefully input the alphanumeric code right into the supplied text field. Accuracy is essential to guarantee the code is recognized and the incentives are truly your own.

- Submit or Verify: After going into the code, submit or validate the redemption. Experience the adventure as the game acknowledges your code, quickly granting you accessibility to the connected benefits.

- Authorities Social Media: Regularly check and comply with the game's official social networks accounts for the most up to date news, updates, and unique codes. Developers typically drop codes as a token of admiration for their devoted player base.

- Disharmony Communities: Dive into the vivid world of the game's Disharmony web server. Developers often engage with the area right here, sharing codes, understandings, and engaging in direct conversations with players.

- Online forums and Websites: Engage yourself in the game's main online forums or devoted community web sites. These spaces frequently come to be hubs for gamers and developers to share codes, approaches, and experiences.

- Expiration Dates: Watch on the expiration days associated with codes. Some codes may have a minimal time window for redemption, adding an element of urgency to the experience.

- Redemption Limitations: Understand any restrictions on code redemption. Some codes may have restrictions on the variety of times they can be utilized or may be limited to details areas or systems.

- Q: How often are new codes released?

- A: The frequency of code releases differs and is commonly tied to the game's advancement cycle, unique events, or neighborhood milestones. Stay tuned to main news for the current information.

- Q: Can I share codes with other players?

- A: In many cases, codes are meant for single-use and need to not be shared publicly. Sharing codes might go to the discernment of the game designer, and breaching code-sharing plans could lead to repercussions.

Where to Locate Verilog Simulation Example

Discovering Verilog Simulation Example entails exploring various networks where developers share these digital tricks with the area. Expand your horizons and keep an eye out in the adhering to locations:

Code Expiry and Limitations

Verilog Simulation YouTube

Verilog Simulation YouTube

While the possibility of receiving special rewards through codes is thrilling, it's necessary to bear in mind particular aspects to take advantage of your gaming experience:

Verilog Simulation

Verilog Simulation

[desc-9]

[desc-7]

Frequently Asked Questions (FAQs)

Conclusion

Verilog Simulation Example are a vibrant component that enhances the gaming experience by giving players with special incentives. Remain attached through authorities channels and area areas to ensure you don't miss out on the newest codes for your preferred games, and allow the electronic journeys proceed!

Verilog Simulation Basics Javatpoint

Verilog Simulation

Check more sample of Verilog Simulation Example below

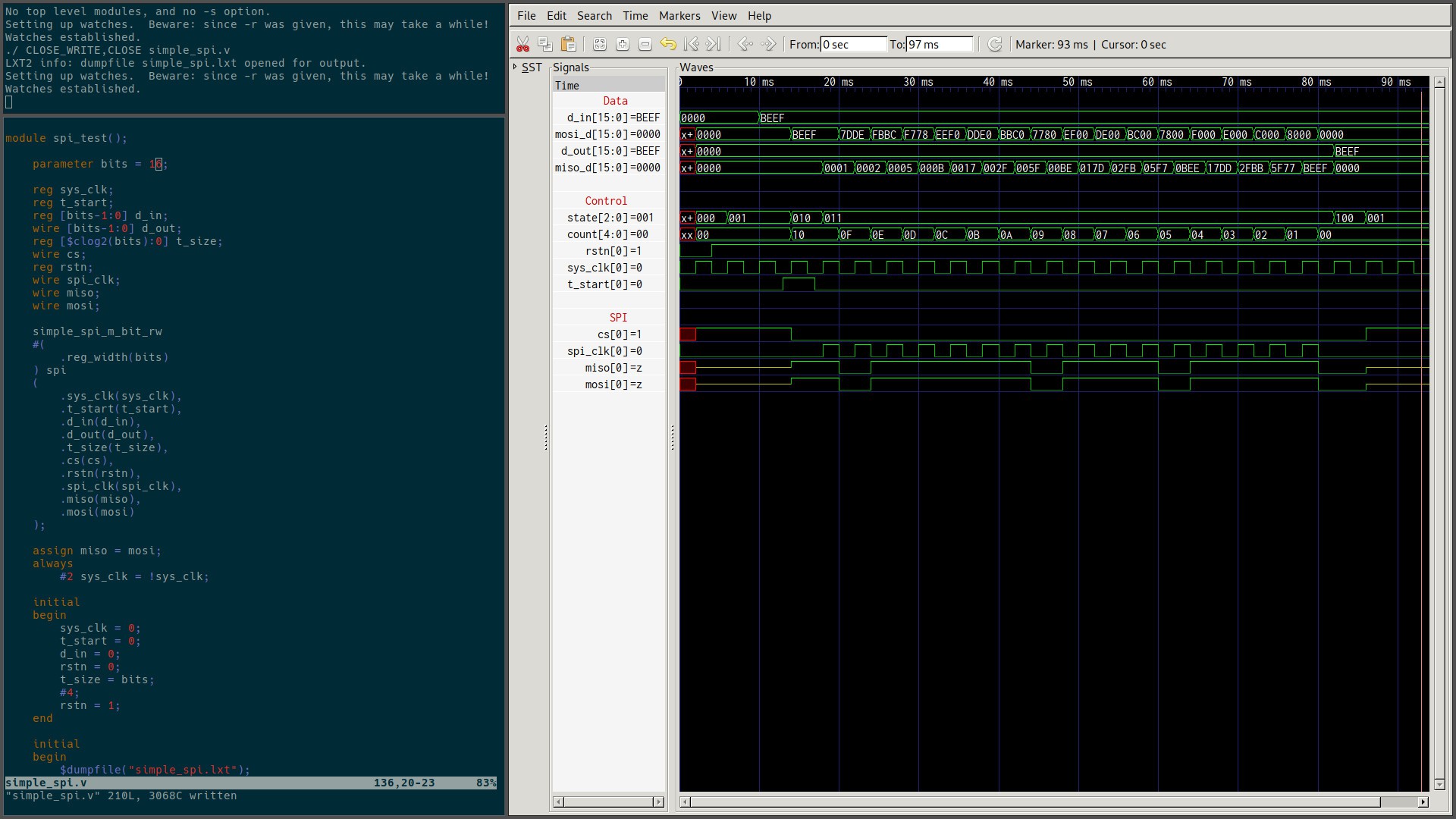

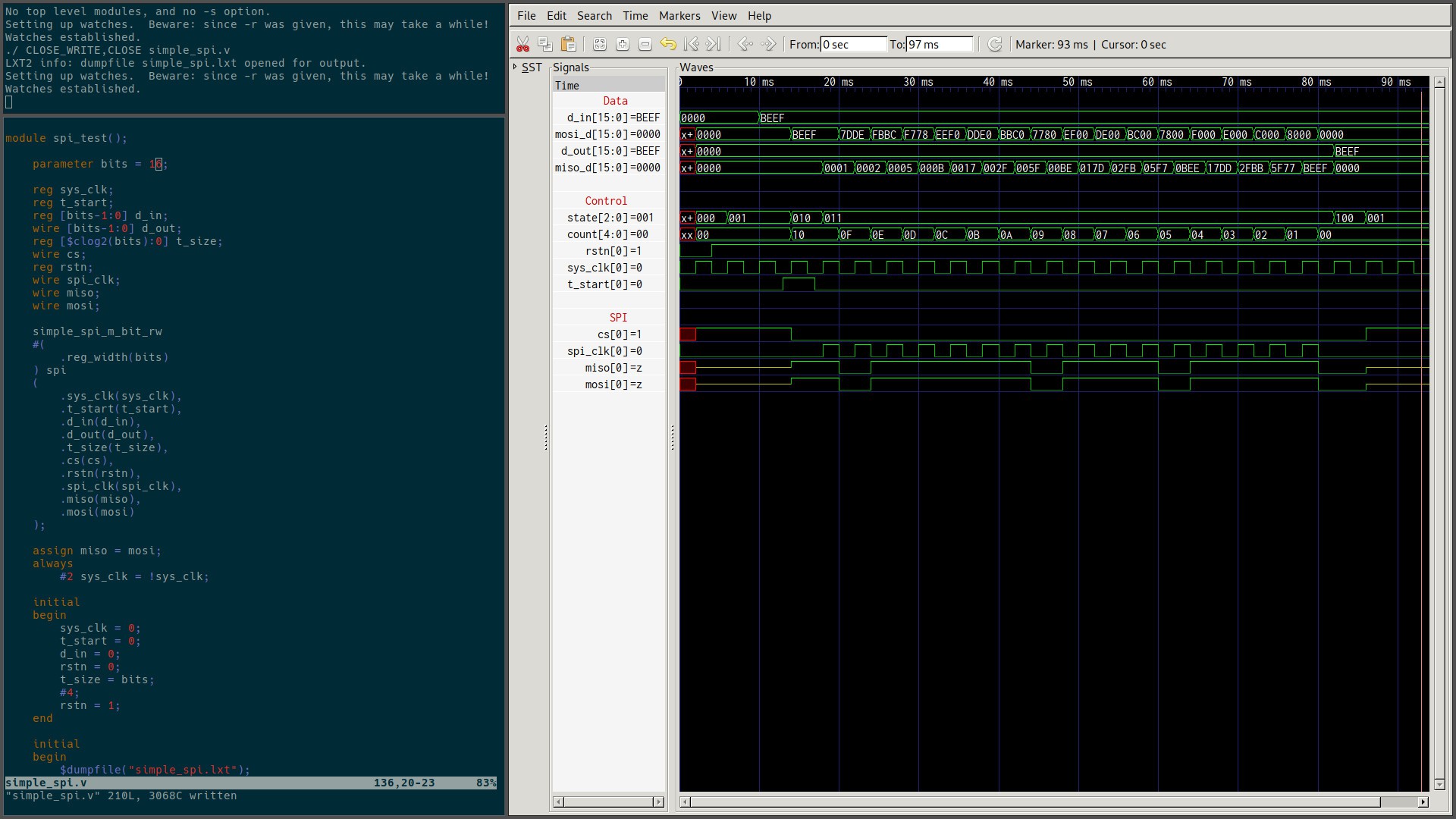

Verilog How To Debug After Implementation My Code That Works

Verilog Simulation

Verilog Simulation Basics Javatpoint

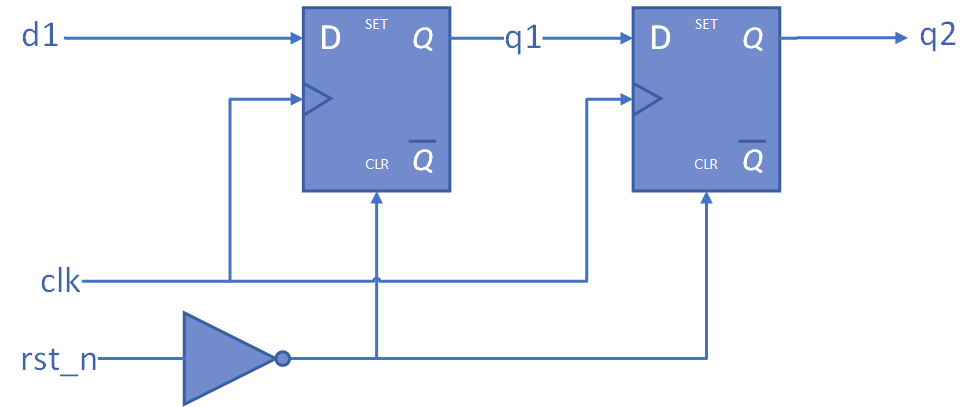

Verilog Always Block For RTL Modeling Verilog Pro

Tutorial 33 Verilog Code Of Serial In Parallel Out Shift Register

Verilog Simulation Tools Details Hackaday io

[desc-1]

[desc-2]

Verilog Always Block For RTL Modeling Verilog Pro

Verilog Simulation

Tutorial 33 Verilog Code Of Serial In Parallel Out Shift Register

Verilog Simulation Tools Details Hackaday io

Verilog lang GitHub Topics GitHub

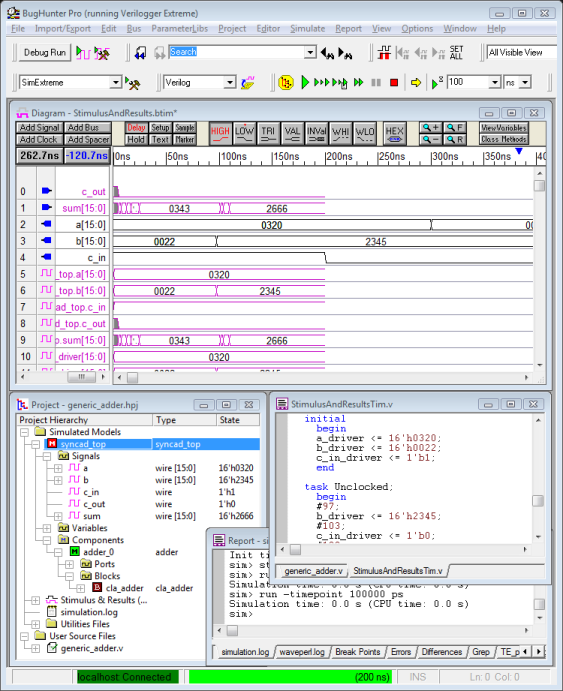

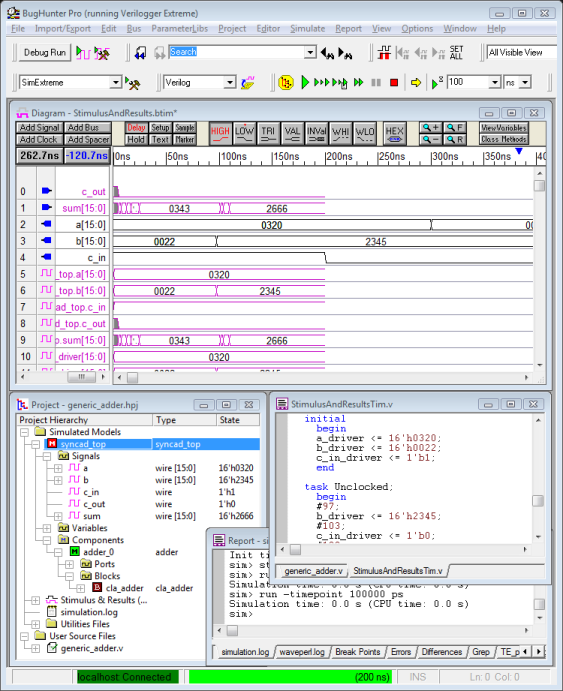

Verilog Simulator Verilog Compiler Synapticad

Verilog Simulator Verilog Compiler Synapticad

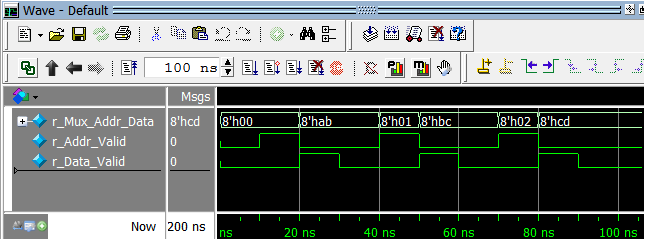

Task Verilog Example